微纳加工

为什么最新的3nm和2nm芯片如此强大?背后的核心技术就是‘光刻’。光刻技术决定了芯片的精度,而EUV光刻的突破让摩尔定律得以延续。本文将带你深入了解光刻加工的全过程,从掩膜设计到纳米级精度的实现。

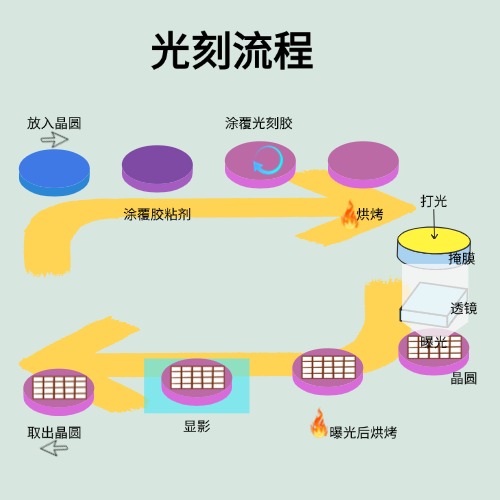

光刻技术是指利用紫外光、极紫外光(EUV)或电子束等高精度曝光方法,将电路图案转移到硅片上的过程。其主要流程包括:

l掩膜设计(Mask Design):设计光掩膜(Photomask),定义芯片电路图案。

l光刻胶涂覆(Photoresist Coating):在晶圆表面均匀涂覆光刻胶。

l曝光(Exposure):使用光学系统将掩膜图案转移到光刻胶层上。

l显影(Development):去除被曝光或未曝光部分的光刻胶,形成电路图案。

l蚀刻(Etching):将显影后图案转移到晶圆表面。

l去胶(Photoresist Removal):清除残余光刻胶,完成图案转移。

光刻工艺的核心目标是提高分辨率、减少缺陷、提升对准精度,从而实现更小的晶体管尺寸。

掩膜(Mask)是光刻工艺的核心组件,相当于芯片的“模具”。高精度掩膜需要考虑:

l光学补偿(OPC,Optical Proximity Correction):修正光学畸变,使图案成像更准确。

l相移掩膜(PSM,Phase Shift Mask):通过相位调制提高分辨率。

l双重曝光(Double Patterning):通过多步光刻提高图案密度。

l缩短波长:从193nm浸没式光刻到13.5nm EUV光刻,不断提升分辨率。

l增大数值孔径(NA):提高透镜系统的光收集能力,如高NA EUV光刻。

l优化光学系统:利用计算光刻(Computational Lithography)优化掩膜图案。

光刻胶(Photoresist)是光刻工艺的核心材料,主要分为正胶和负胶:

正胶(Positive Resist):曝光部分溶解,未曝光部分保留。适用于高分辨率光刻。

负胶(Negative Resist):曝光部分固化,未曝光部分去除。适用于特殊工艺。

目前最先进的EUV光刻胶需要具备:

l高分辨率(亚10nm工艺)

l低光敏反应噪声

l高化学稳定性

常见的曝光技术包括:

l深紫外(DUV)光刻:采用193nm ArF光源,适用于7nm及以上制程。

l极紫外(EUV)光刻:采用13.5nm EUV光源,可实现5nm及以下制程。

l电子束直写(EBL):适用于研究级光刻,精度可达2nm,但产能较低。

l光学对准(Alignment):通过干涉测量提高对准精度。

l自适应校正(Adaptive Optics):实时修正光学系统误差。

l机器学习优化:利用AI分析光刻偏差,提高曝光精度。

l分辨率极限:EUV光刻仍然受光学系统限制,难以突破2nm节点。

l掩膜精度要求更高:EUV掩膜成本极高,容易出现缺陷。

l光刻胶的稳定性:现有光刻胶在EUV环境下的耐受性仍有待提升。

l高NA EUV光刻(数值孔径 > 0.5):预计用于2nm及以下制程。

l纳米压印光刻(NIL):成本低,但产能受限,适用于特殊应用。

l分子光刻(Molecular Lithography):结合DNA自组装,实现亚1nm图案。

lEUV光刻技术的成熟化:未来EUV光刻将继续优化,提高良率,降低成本。

l后EUV时代:X射线光刻? 研究探索更短波长的X射线光刻以进一步提高分辨率。

lAI辅助光刻:利用深度学习优化光刻参数,提高生产效率。

目前,ASML、Nikon、Canon等光刻机制造商正加速研发更高精度的光刻设备。预计未来:

l3nm、2nm制程将大规模商用,推动半导体技术进步。

l光刻设备成本将继续上升,先进EUV光刻机单价已超过3亿美元。

光刻技术是推动半导体产业发展的核心驱动力。从掩膜设计到纳米级精度的实现,每个环节都对芯片的性能和良率起着关键作用。随着EUV光刻的不断进步和新型光刻技术的探索,未来的半导体制程将继续向更高集成度、更低功耗、更强算力方向迈进。光刻技术的突破不仅影响着芯片行业,也决定着人工智能、5G、自动驾驶等前沿科技的发展。未来,随着高NA EUV光刻的应用和AI辅助光刻的成熟,半导体行业将迎来新的变革。

苏州原位芯片科技有限责任公司©版权所有 苏ICP备15018093号-6 苏公网安备 32059002002439号 网站地图